I'm a riscv amateur.

I want to generate misaligned exception but it doesn't work.

I test qemu v6.2 and v7.2, both of them can't work.

qemu-system-riscv32 -version

QEMU emulator version 6.2.0 (Debian 1:6.2+dfsg-2ubuntu6.6)

Copyright (c) 2003-2021 Fabrice Bellard and the QEMU Project developers

/home/eric/qemu/build_v7.2/qemu-system-riscv32 --version

QEMU emulator version 7.2.0 (v7.2.0)

Copyright (c) 2003-2022 Fabrice Bellard and the QEMU Project developers

for fetch misalgiend exception, I refer Volume I: RISC-V User-Level ISA V2.2

「An instruction address misaligned exception is generated on a taken branch or unconditional jump if the target

address is not four-byte aligned.」

address is not four-byte aligned.」

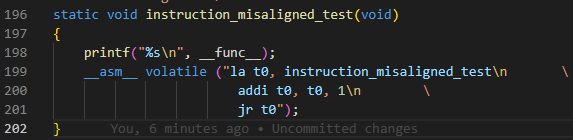

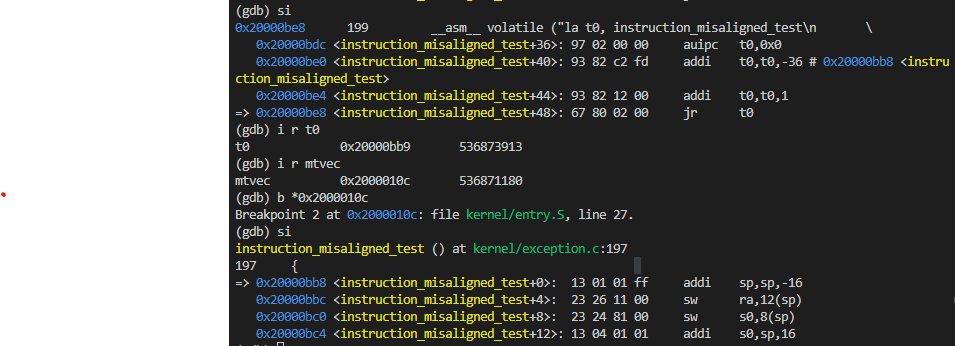

So I use jr with a unaligned target address but it seem automatically align address.

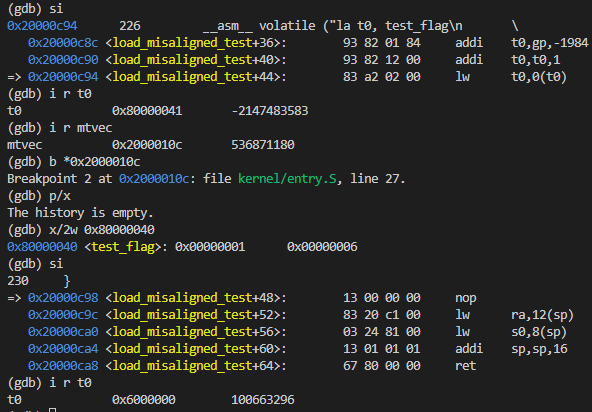

for load/store misaligned exception, I use lw, sw for a unaligned address,

but it can read/write unaligned memory...

Thanks,

Eric Chan